|

DOSBox-X

|

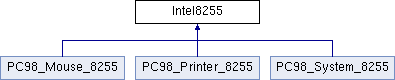

Intel 8255 base emulation class. More...

#include <8255.h>

Public Types | |

| enum | { PortA = 0, PortB = 1, PortC = 2 } |

Public Member Functions | |

| Intel8255 () | |

| Constructor. | |

| virtual | ~Intel8255 () |

| Destructor. | |

| void | reset (void) |

| Reset state (as if activating reset signal) | |

| void | ackPortA (void) |

| External acknowledgement of port A. | |

| void | ackPortB (void) |

| External acknowledgement of port B. | |

| virtual void | strobePortA (void) |

| Strobed Input (latch to port A) | |

| virtual void | strobePortB (void) |

| Strobed Input (latch to port B) | |

| uint8_t | readPortA (void) |

| Called when CPU reads port A. | |

| uint8_t | readPortB (void) |

| Called when CPU reads port B. | |

| uint8_t | readPortC (void) |

| Called when CPU reads port C. | |

| uint8_t | readControl (void) |

| Called when CPU reads control port. | |

| uint8_t | readByPort (const uint8_t p03) |

| Called when CPU reads from the chip. | |

| void | writePortA (const uint8_t data, uint8_t mask=0xFFU) |

| Called when CPU writes port A. | |

| void | writePortB (const uint8_t data, uint8_t mask=0xFFU) |

| Called when CPU writes port B. | |

| void | writePortC (const uint8_t data, uint8_t mask=0xFFU) |

| Called when CPU writes port C. | |

| void | writeControl (const uint8_t data) |

| Called when CPU writes control port. | |

| void | writeByPort (const uint8_t p03, const uint8_t data) |

| Called when CPU writes to the chip. | |

| virtual uint8_t | inPortA (void) const |

| Called by 8255 emulation to latch from port A pins. | |

| virtual uint8_t | inPortB (void) const |

| Called by 8255 emulation to latch from port B pins. | |

| virtual uint8_t | inPortC (void) const |

| Called by 8255 emulation to latch from port C pins. | |

| virtual void | outPortA (const uint8_t mask) |

| Called by 8255 emulation when latching to port A pins. | |

| virtual void | outPortB (const uint8_t mask) |

| Called by 8255 emulation when latching to port B pins. | |

| virtual void | outPortC (const uint8_t mask) |

| Called by 8255 emulation when latching to port C pins. | |

| void | updateINTR_A (void) |

| Internal 8255 emulation code to update INTR A signal. | |

| void | updateINTR_B (void) |

| Internal 8255 emulation code to update INTR B signal. | |

| void | checkINTR_A (void) |

| Internal 8255 emulation code to check INTR A change and dispatch signal. | |

| void | checkINTR_B (void) |

| Internal 8255 emulation code to check INTR B change and dispatch signal. | |

| virtual void | sigINTR_A (void) |

| Called by 8255 emulation when INTR A signal changes to dispatch signal. | |

| virtual void | sigINTR_B (void) |

| Called by 8255 emulation when INTR B signal changes to dispatch signal. | |

| const char * | getName (void) const |

| Retrieve the name of this chip (for debug/UI purposes) | |

| const char * | pinName (const unsigned int port, const unsigned int i) const |

| Retrieve the name of a pin on the chip related to port A, B, or C (what it's connected to) (for debug/UI purposes) | |

| const char * | portName (const unsigned int port) const |

| Retrieve the name of a port (A, B, or C) (for debug/UI purposes) | |

Public Attributes | |

| uint8_t | portAWriteMask = 0 |

| Port A write mask. Controls which bits are writeable. | |

| uint8_t | portBWriteMask = 0 |

| Port B write mask. Controls which bits are writeable. | |

| uint8_t | portCWriteMask = 0 |

| Port C write mask. Controls which bits are writeable. | |

| const char * | ppiName |

| PPI chip name (for debug/UI purposes) | |

| const char * | pinNames [3][8] = {} |

| Pin names (for debug/UI purposes) | |

| const char * | portNames [3] = {} |

| Port names (for debug/UI purposes) | |

| uint8_t | latchOutPortA = 0 |

| Port A output latch. | |

| uint8_t | latchOutPortB = 0 |

| Port B output latch. | |

| uint8_t | latchOutPortC = 0 |

| Port C output latch. | |

| uint8_t | mode = 0 |

| PPI mode byte. | |

| bool | IBF_A = false |

| Input Buffer Full, port A contains information (port A, Mode 1) | |

| bool | IBF_B = false |

| Input Buffer Full, port B contains information (port B, Mode 1) | |

| bool | OBF_A = false |

| Output Buffer Full, port A contains information for the external device (port A, Mode 1) | |

| bool | OBF_B = false |

| Output Buffer Full, port B contains information for the external device (port B, Mode 1) | |

| bool | INTR_A = false |

| Interrupt Request A (to the microprocessor) | |

| bool | INTR_B = false |

| Interrupt Request B (to the microprocessor) | |

| bool | pINTR_A = false |

| Previous Interrupt Request A state (for change detection) | |

| bool | pINTR_B = false |

| Previous Interrupt Request B state (for change detection) | |

| bool | INTE_1 = false |

| Interrupt 1 enable (mode 2) | |

| bool | INTE_2 = false |

| Interrupt 2 enable (mode 2) | |

| bool | INTE_A = false |

| Interrupt A enable. | |

| bool | INTE_B = false |

| Interrupt B enable. | |

Static Protected Member Functions | |

| static const char * | nil_if_null (const char *str) |

| Return string "str", or "" (empty string) if str == NULL. | |

Intel 8255 base emulation class.

Intel 8255 Programmable Peripheral Interface emulation class. The base class handles the functions and register I/O to emulate the 8255, while the subclass implements behavior of hardware attached to the 8255.

All emulation is written to follow Intel's datasheet as closely as possible.

NOTE: Mode 2 emulation has NOT been tested yet!

| anonymous enum |

1.8.0

1.8.0